# HTS200N03

P<sub>-</sub>1

#### 30V N-Ch Power MOSFET

#### Feature

High Speed Power Switching, Logic Level Enhanced Avalanche Ruggedness 100% UIS Tested, 100% Rg Tested Lead Free, Halogen Free

| $V_{DS}$                          |                      | 30   | V |

|-----------------------------------|----------------------|------|---|

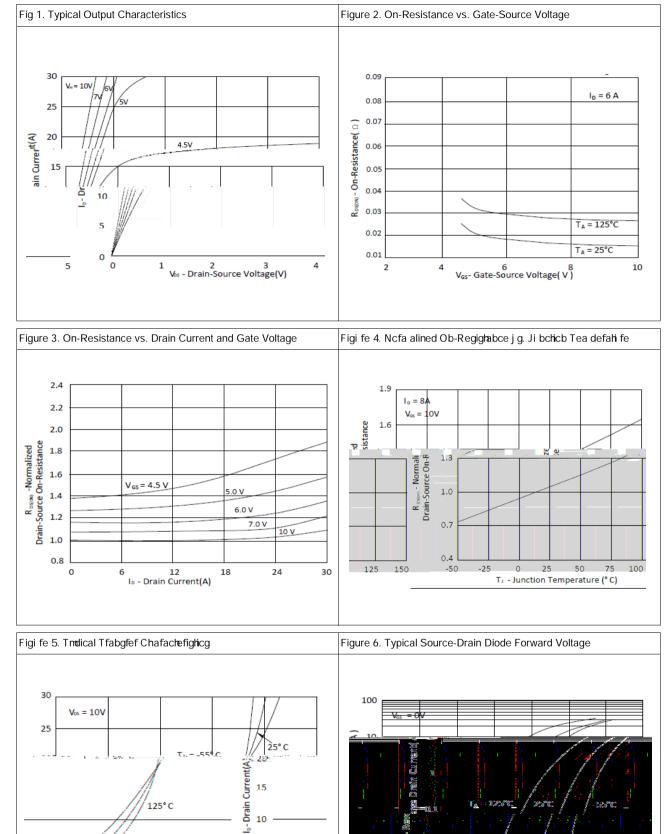

| $R_{DS(on),typ}$                  | V <sub>GS</sub> =10V | 15.5 | m |

| I <sub>D</sub> (Sillicon Limited) |                      | 9.5  | Α |

### Application

Hard Switching and High Speed Circuit DC/DC in Telecoms and Inductrial

| Part Number | Package | Marking  |

|-------------|---------|----------|

| HTS200N03   | SOIC-8  | TS200N03 |

Absolute Maximum Ratings at T<sub>i</sub>=25 (i blegg chefk ige gdecified)

| Parameter                                  | Symbol                            | Conditions                  | Value     | Unit |

|--------------------------------------------|-----------------------------------|-----------------------------|-----------|------|

| Continuous Drain Current (Silicon Limited) | I <sub>D</sub>                    | T <sub>A</sub> =25          | 9.5       | Α    |

|                                            |                                   | T <sub>A</sub> =70          | 7.5       |      |

| Drain to Source Voltage                    | $V_{DS}$                          | -                           | 30        | V    |

| Gate to Source Voltage                     | $V_{GS}$                          | -                           | ±20       | V    |

| Pulsed Drain Current                       | I <sub>DM</sub>                   | -                           | 38        | Α    |

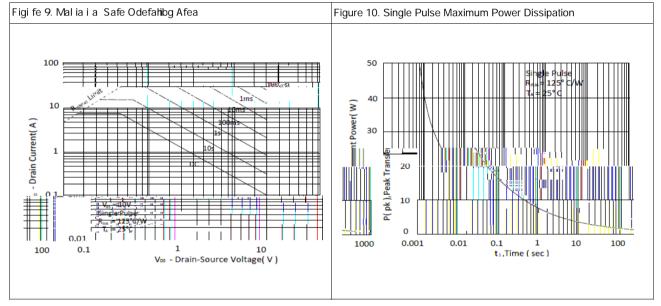

| Avalanche Energy, Single Pulse             | E <sub>AS</sub>                   | L=0.1mH, T <sub>C</sub> =25 | 3.2       | mJ   |

| Power Dissipation                          | $P_{D}$                           | T <sub>A</sub> =25          | 2.5       | W    |

| Operating and Storage Temperature          | T <sub>J</sub> , T <sub>stg</sub> | -                           | -55 to150 |      |

### **Absolute Maximum Ratings**

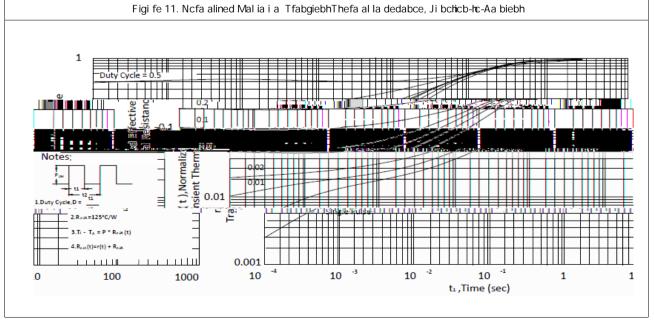

| Parameter                           | Symbol          | Max | Unit     |

|-------------------------------------|-----------------|-----|----------|

| Thermal Resistance Junction-Ambient | R <sub>JA</sub> | 50  | <i>W</i> |

| Thermal Resistance Junction-Case    | R <sub>JC</sub> | 25  | <i>W</i> |

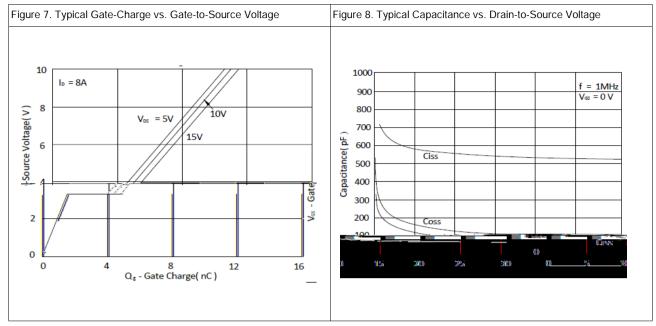

Total Gate Charge

Q<sub>g</sub>(4.5V)

6.1 nC 1.6

10

- Gate-Source Voltage(V)

Ver 1.0 Sep. 2017

(0).22

(0)./4

(0).65

1.5

10

| Inductive switching Test |                          |                          |

|--------------------------|--------------------------|--------------------------|

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          | Gate Cha                 | arge Test                |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          | Halaman and Implications | Curitabile e // UC) Tank |

|                          | Uclamped Inductive       | Switching (UIS) Test     |

| VE                       |                          |                          |

| VL                       |                          |                          |

| 1                        | V <sub>DD</sub> +        |                          |

| V                        | DUT T-                   |                          |

| V <sub>GS</sub>          |                          |                          |

|                          | 5: - 5                   |                          |

| Diode Recovery Test      |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

|                          |                          |                          |

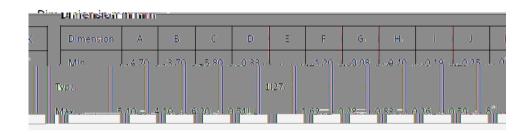

## Package Outline

### SOIC-8, 8 leads